Genre: eLearning | MP4 | Video: h264, 1280×720 | Audio: AAC, 44.1 KHz

Language: English | Size: 1.17 GB | Duration: 2h 41m

PC653EC || DSDV || Electronics and Communication Engineering || 6th SEM || Bachelor of Engineering

What you’ll learn

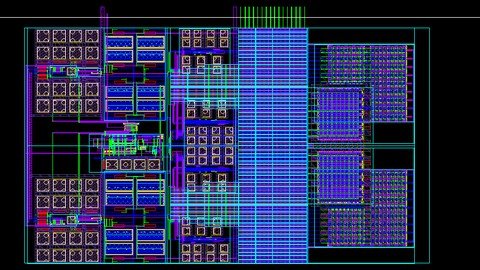

1. Describe verilog HDL and develop digital circuits using gate level and data flow modeling

2. Develop verilog HDL code for digital circuits using switch level and behavioral modeling

3. Design and develop of digital circuits using Finite State Machines(FSM)

4. Perform functional verification of above designs using Test Benches.

5. Appreciate the constructs and conventions of the verilog HDL programming in gate level and data flow modeling.

6. Generalize combinational circuits in behavioral modeling and concepts of switch level modeling

7. Design and analyze digital systems and finite state machines.

8. Perform functional verification by writing appropriate test benches.

Requirements

Digital Electronics

Switching Theory and Logic Design

Description

Course Objectives

1. Describe Verilog HDL and develop digital circuits using gate level and data flow modeling

2. Develop Verilog HDL code for digital circuits using switch level and behavioral modeling

3. Design and develop digital circuits using Finite State Machines(FSM)

4. Perform functional verification of the above designs using Test Benches.

5. Implementation of experiments on FPGA/CPLD boards.

Course Outcomes: The students able to

1. Appreciate the constructs and conventions of the Verilog HDL programming in gate level and data flow modeling.

2. Generalize combinational circuits in behavioral modeling and concepts of switch level modeling

3. Design and analyze digital systems and finite state machines.

4. Perform functional verification by writing appropriate test benches.

5. Implement designs on FPGA/CPLD boards.

List of Experiments

Write the Code using VERILOG, Simulate and synthesize the following

1. Write structural and dataflow Verilog HDL models for

a) 4-bit ripple carry adder.

b) 4-bit carry Adder – cum Subtractor.

c) 2-digit BCD adder / subtractor.

d) 4-bit carry look-ahead adder

e) 4-bit comparator

2. Write a Verilog HDL program in Hierarchical structural model for

a) 16:1 mux realization using 4:1 mux

b) 3:8 decoder realization through 2:4 decoder

c) 8-bit comparator using 4-bit comparators and additional logic

3. Write a Verilog HDL program in the behavioral model for

a) 8:1 mux

b) 3:8 decoder

c) 8:3 encoder

d) 8-bit parity generator and checker

4. Write a Verilog HDL program in structural and behavioral models for

a) 8 bit asynchronous up-down counter

b) 8 bit synchronous up-down counter

5. Write a Verilog HDL program for a 4-bit sequence detector through Mealy and Moore state machines.

6. Write a Verilog HDL program for traffic light controller realization through the state machine.

7. Write a Verilog HDL program for vending machine controller through the state machine.

8. Write a Verilog HDL program in the behavioral model for an 8-bit shift and add a multiplier.

9. Write a Verilog HDL program in the structural model for the 8-bit Universal Shift Register.

10. Write a Verilog HDL program for implementation of data path and controller units

a) Serial Adder

b) ALU

Who this course is for

VI SEM ECE Students who want to Perform Digital System Design using Verilog HDL Lab Experiments

VLSI Beginners

Password/解压密码www.tbtos.com