Video: .mp4 (1280×720, 30 fps(r)) | Audio: aac, 44100 Hz, 2ch | Size: 2.96 GB

Genre: eLearning Video | Duration: 69 lectures (7 hour, 3 mins) | Language: English

All about AXI Slave Lite and AXI Stream Interface

What you’ll learn

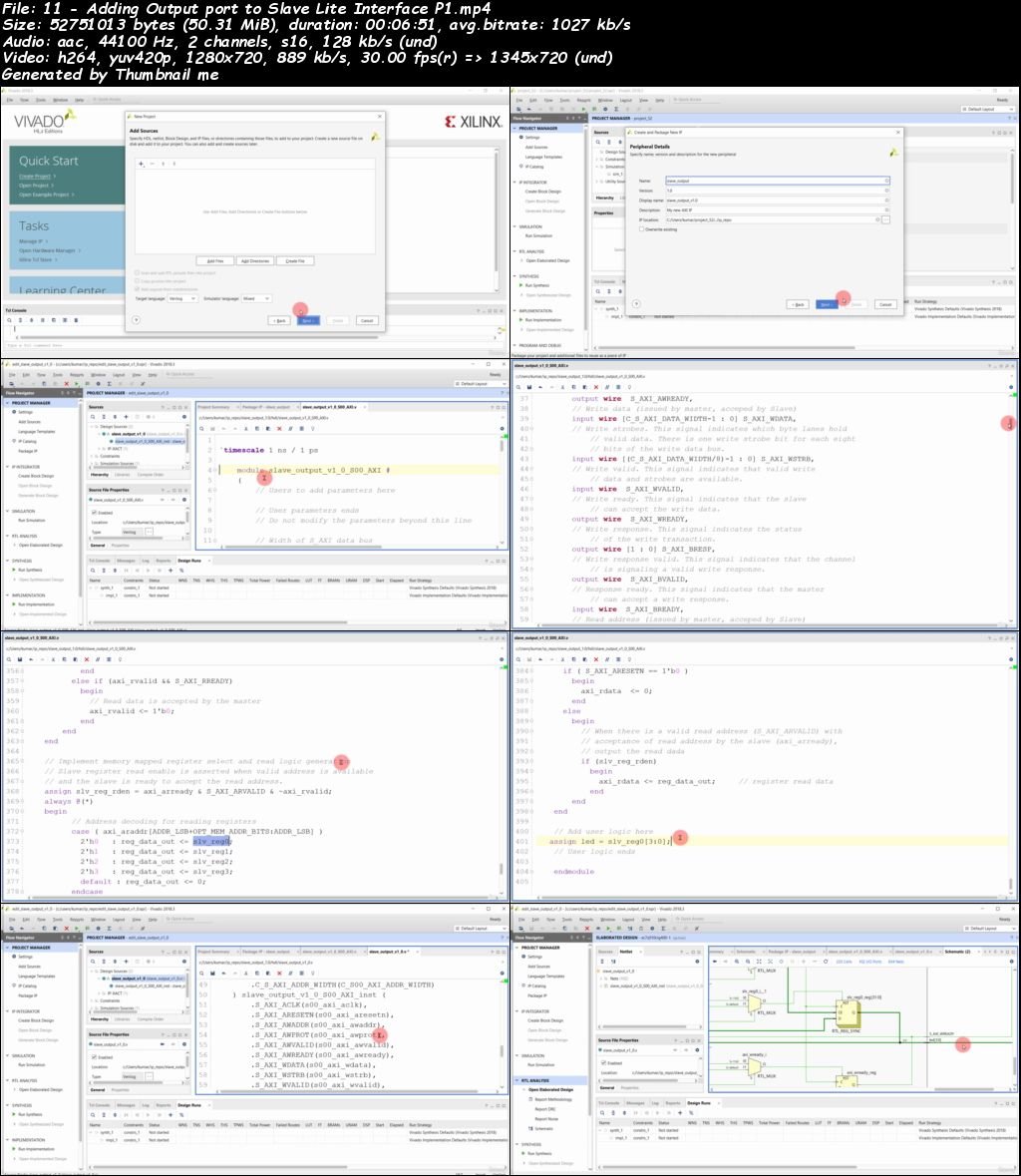

Building custom AXI Slave Lite Interface

Handling Interrupts with Custom AXI Slave Lite Interface

Creating Custom AXI Stream Interface with Vivado Template

Building Custom AXI Stream Interface with Verilog RTL

Writing Drivers for Custom AXI Interface

Interfacing of Custom AXI Interface with Zynq devices

Requirements

Fundamentals of Xilinx Drivers and Embedded Design Flow

Description

As system complexities are growing day by day, the Zynq device alone is incapable of providing the same performance and the Pure RTL module or Programmable logic (PL) needs to be integrated along with the Zynq. As Zynq works with Advanced Extensible Peripheral (AXI), it becomes mandatory for FPGA engineers to gain a fundamental understanding of adding AXI Interface to the Verilog RTL. The AXI4 offers different variants to fit diverse application needs. Understanding of the simpler variants such as AXI Lite and AXI Stream Interface lays a foundation for building an understanding of the complex AXI4 variant such as AXI Full.

This course focuses on the usage of the Vivado IP Integrator and Vivado RTL integration for building the custom AXI interface for pure Verilog modules. There are four ways to achieve the addition of the AXI interface to the Verilog RTL viz. Using Vivado IP Packager, Vivado RTL Integration, Using System Generator, Using Vivado HLS. The course discusses two methodologies viz. Vivado IP Packager and Vivado RTL Integration in details with a simple example along with the demonstration of the integration of the created IP with the Zynq device. It will also discuss the creation of some basic device drivers, showing how software can be written to access the registers on the custom peripheral.

Who this course is for

Anyone wish to build expertise in designing Custom AXI interface for Zynq Devices

Developing Hardware Accelerators with Verilog RTL

Password/解压密码www.tbtos.com

转载请注明:0daytown » Building Custom AXI Interface Peripherals for ZYNQ Devices