Genre: eLearning | MP4 | Video: h264, 1280×720 | Audio: AAC, 48.0 KHz

Language: English | Size: 3.36 GB | Duration: 5h 2m

Build a strong Verilog language foundation by implementing combinational / sequential digital circuits and testbenches

What you’ll learn

Master the basics of Verilog language for designing synthesizable digital circuits for ASIC / FPGA

Differentiate between Verilog structural / dataflow / behavioral design styles and how / when to use them in Digital Design and Verification

Implement combinational and sequential digital circuits using Verilog HDL starting from schematics or functional specifications

Create and simulate a Verilog testbench for a digital circuit starting from its functional specifications

Examine the behavior of a digital circuit receiving stimulus in a testbench, using an industry-level simulator (free for academic purposes)

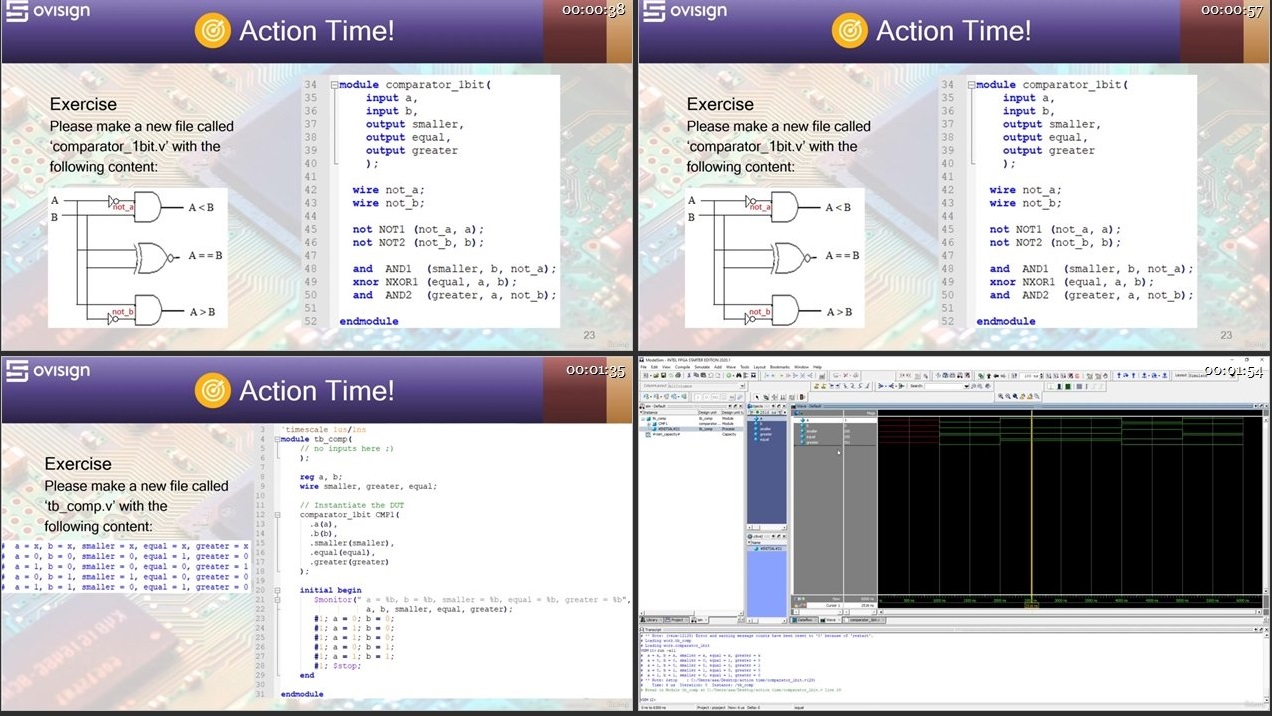

Explicit visual explanations for the 80+ downloadable code examples, circuits, and testbenches offering you increased retention and accelerated learning

Description

Are you a beginner or an enthusiastic hobbyist interested in digital circuits design using the Verilog Hardware Description Language? Did you try to learn Verilog HDL before, but found it very challenging? Are you curious if you have what it takes to become a digital chip designer? Then you’re in the right place!

Verilog Hardware Description Language easy as A,B,C

You’ll learn the basics of digital circuits theory and we’ll focus most of our energy on implementing practical coding examples with real digital circuits using Verilog. You will graduate this course with a strong foundation in Verilog HDL for both Digital Design and Functional Verification.

From the Digital Design perspective, you’ll be able to:

start from a digital circuit diagram / schematic and implement synthesizable Verilog code for ASIC / FPGA

start from a functional description and implement synthesizable Verilog code for ASIC / FPGA

From the Functional Verification perspective, you’ll be able to:

understand a functional description of a digital circuit and create stimuli for it

implement a self-checking testbench to validate the functionality of a digital circuit

You will easily differentiate between different Verilog coding styles (structural, dataflow, behavioral) and how to use them to design synthesizable digital circuits. You’ll see just how easy modeling digital circuits using Verilog is!

At the end of the course you’ll master Verilog industry-level coding techniques to get the best results for digital design or verification.

Learn how to use an industry-level Verilog HDL simulator

Simulations are a critical part in designing modern digital chips, thus you will install and learn how to use Modelsim – Intel FPGA Edition (free version for academic purpose). You will be able to create projects, simulate your Verilog code, and interpret the outputs using an world-class simulator.

Course Overview

This course is tailored for beginners who are interested in digital microelectronics, digital circuit design and verification. The course contains more than 158 bite-sized lectures out of which more than half are hands-on exercises labeled Action Time. Each Action Time has downloadable resources which you can simulate immediately using Modelsim. Most of these sections also contain challenges for you, so you’ll write extra code that extends beyond the initial functionality.

Your first Verilog examples will be similar to a normal programming language (like C) to learn the operators, and, step-by-step, we’ll advance together to the Hardware Description Language constructs, where Verilog procedures execute in parallel.

You’ll learn how to use Verilog for combinational and sequential logic and how to combine the Structural / Dataflow / Behavioral coding styles to obtain digital circuits with a specific functionality. Your circuits will get more complex as you advance, some of them being composed of a hierarchy of sub-circuits.

Verilog combinational circuits you will implement during the course : logic gates, adders, comparator, binary encoder / decoder, priority encoder, multiplexers / de-multiplexers, seven segment display decoder, Arithmetical Logical Unit (ALU), etc…

Verilog sequential circuits you will implement during the course: flip-flops, latches, shift registers (PIPO, PISO, SIPO, SISO), Linear Feedback Shift Registers, synchronous counters, frequency dividers, Sequence Detector etc…

Next, you’ll experiment with Verilog functions and tasks and how to use them in testbenches and design.

In the final chapters you will design memories (SRAM and ROM), Finite State Machines, and more complex circuits like a FIFO and even a data encryption module.

A workflow with destination SUCCESS!

We start from real engineering problems and understand how a digital circuit solves that problem.

You are presented a real digital circuit, how it is used in the real world, then how to model and test it using Verilog.

You simulate it using Modelsim, and next I walk you through the results interpretation.

We do this process together every single time…. I explain the story behind the Verilog code so that, at the end of the course, you will be able to write the Verilog code behind the story.

Why learn Verilog HDL?

Chances are more than 50% that all the chips in the devices around you were designed with Verilog.

Working as a Digital Design or a Functional Verification engineer means to design today the technologies of tomorrow. This translates into having an exciting and challenging job with a great impact in the world. Since less than 2% of engineers choose this path and the semiconductor industry has never been busier, I’m pretty sure you will find yourself a good place in it.

Verilog is a good foundation for learning SystemVerilog, which is a very popular object-oriented design and verification language in the semiconductor industry.

Why did I create this course?

As an engineering student, I found it quite challenging to learn Verilog because it has a very steep learning curve and you need lots of know-how to be able to run even a simple example. Because of this, most students give up learning Verilog for a career in Digital Design or Verification and this also negatively impacts their academic results.

After 10+ years of industry experience, thousands of hours in Verilog, and academic research, I feel I’ve found the missing puzzle pieces that I didn’t have back in the days. This course will show you the beauty and simplicity of digital circuits design using Verilog!

Ready? Set… GO!

Thank you for your interest in Verilog HDL for Digital Circuits Design and Functional Verification!

Ready to embark on your journey in mastering the basics of Verilog HDL for digital design and verification? Let’s start this wonderful adventure!

Who this course is for:

Computer Science, Electronics, Telecommunications, and Microelectronics students who want to learn Verilog for their projects and faculty assignments

Electronics and Microelectronics hobbyists who want to learn the Verilog Hardware Description Language

Beginners who aspire to a career as a Digital Design Engineer or a Functional Verification Engineer

Beginners in digital microelectronics and digital circuits design curious about the Verilog Hardware Description language

Download rapidgator

https://rg.to/file/51af6a54e10186c50c2a9222aec37a90/Verilog_HDL_Fundamentals_for_Digital_Design_and_Verification.part1.rar.html

https://rg.to/file/4e10c5e12329095c0964387f830f7ec2/Verilog_HDL_Fundamentals_for_Digital_Design_and_Verification.part2.rar.html

https://rg.to/file/99ac228274a1616ae81d9be617c962a8/Verilog_HDL_Fundamentals_for_Digital_Design_and_Verification.part3.rar.html

https://rg.to/file/32a34b1dbed0da1d4c6cf6e50fd455c5/Verilog_HDL_Fundamentals_for_Digital_Design_and_Verification.part4.rar.html

https://rg.to/file/044bc6160fe3a645a20fc5333c6a16f1/Verilog_HDL_Fundamentals_for_Digital_Design_and_Verification.part5.rar.html

https://rg.to/file/84a1bce4ae8d97c82954a14eacd6e30d/Verilog_HDL_Fundamentals_for_Digital_Design_and_Verification.part6.rar.html

Download nitroflare

https://nitro.download/view/2C0F06C3D6C80E4/Verilog_HDL_Fundamentals_for_Digital_Design_and_Verification.part1.rar

https://nitro.download/view/F9F4E57A7ACC1B3/Verilog_HDL_Fundamentals_for_Digital_Design_and_Verification.part2.rar

https://nitro.download/view/52FB4AA40BBE062/Verilog_HDL_Fundamentals_for_Digital_Design_and_Verification.part3.rar

https://nitro.download/view/FE0F2A19461A4B6/Verilog_HDL_Fundamentals_for_Digital_Design_and_Verification.part4.rar

https://nitro.download/view/1B01F07C2484154/Verilog_HDL_Fundamentals_for_Digital_Design_and_Verification.part5.rar

https://nitro.download/view/82BDBAD3AF15BB5/Verilog_HDL_Fundamentals_for_Digital_Design_and_Verification.part6.rar

转载请注明:0daytown » Verilog HDL Fundamentals for Digital Design and Verification