Genre: eLearning | MP4 | Video: h264, 1280×720 | Audio: AAC, 44.1 KHz

Language: English | Size: 3.02 GB | Duration: 9h 56m

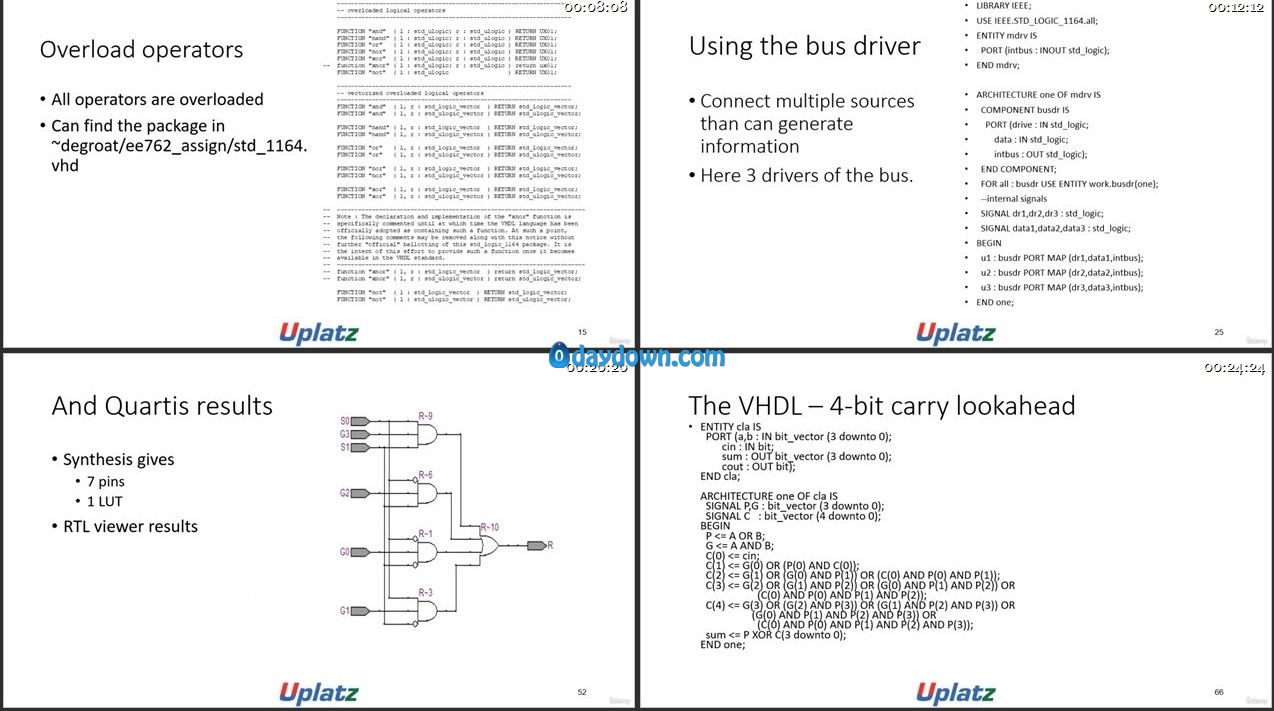

Model & simulate the structure of digital systems with VHDL & Verilog. RTL Systems, FPGA Testing, Design Flows & Tools.

What you’ll learn

Learn fundamental concepts of Digital Design, Design for Testability, Fault Simulation

Understand VHDL and Verilog Programming constructs and their applications

Define State Machines, State Reduction & Assignment, RTL Design

Learn & apply SystemVerilog

Gain experience on Test Benches

Understand FPGA, ASIC/FPGA Testing, FPGA Design Flows & Tools

Description

Uplatz provides this extensive course on Digital System Design with VHDL & Verilog.

The Verilog Hardware Description Language (Verilog HDL) is a language that is used to describe the behavior & structure of electronic circuits, most commonly digital circuits. Verilog HDL is defined by IEEE standards. The common variants include Verilog 1995, Verilog 2001, and the recent SystemVerilog 2005. Verilog HDL is used for designing hardware and for creating test entities to verify the behavior of a piece of hardware. Verilog is facilitated through a variety of EDA tools, including synthesis tools such as various simulation tools, and formal verification tools. Digital Systems Design using Verilog combines logic design concepts, Verilog as a hardware design language, and FPGA implementation to assist the electronics and computer engineering students in mastering the process of developing and testing novel hardware configurations. Verilog, a hardware description language, may be used to incorporate massive and complex digital circuits into hardware (HDL).

Very High-Speed Integrated Circuit Hardware Description Language (VHDL) is a description language used to describe hardware. It is utilized in electronic design automation to express mixed-signal and digital systems, such as ICs (integrated circuits) and FPGA (field-programmable gate arrays). We can also use VHDL as a general-purpose parallel programming language.

In essence, both Verilog and VHDL are the Hardware Description Languages (HDL) that help to describe digital electronic systems. The main difference between Verilog and VHDL is that Verilog is based on C language while VHDL is based on Ada and Pascal languages.

To be effective, a designer who wants to understand these HDL languages must first get familiar with their structure, practice the same in real-world applications, and combine them. Nerds will be able to complete all of these jobs using Design Through Verilog HDL, while seasoned experts will have access to a full resource on this dynamic technology. The VLSI sector creates silicon chips for a variety of applications, including automotive, consumer electronics, medical, IoT, and artificial intelligence. To make the aforesaid gadgets functional, each silicon will contain millions or billions of transistors building complicated logic circuits. The industry’s overall development will be aided by increased demand for chips connected to the fast-rising usage of AI.

This Digital System Design with VHDL & Verilog course covers the creation and implementation of FPGA-based digital systems utilizing the two most prominent hardware description languages, Verilog and VHDL. This course of Digital System & Circuit Design with VHDL & Verilog provides a solid foundation in FPGA concepts, methods, and applications, as well as an introduction of more difficult issues. Real-world examples, ready-to-run code, and low-cost start-to-finish demonstrations are used to highlight key ideas.

The course covers the fundamental tools for designing digital circuits as well as processes for a wide range of digital applications. Digital System Design with VHDL & Verilog is a course that is designed to teach students how to create and successfully simulate their Verilog/VHDL design. We will also be implementing these designs on a Xilinx BASYS 3 or BASYS 2 FPGA development board so that the students can see their designs actually running. This course teaches the delegates from scratch how to turn their digital logic design into VHDL designs that can be simulated in ModelSim or ISim and then implemented on an FPGA development board. With this VHDL & Verilog course, the students will be able to understand the syntax and use of specific VHDL & Verilog HDL terminologies. The course starts with the basic concepts of Design for Testability, Fault Simulation, and then proceeds with understanding of State Machines. This Electronics & Digital Systems design course covers in-depth the structure, syntax, and usage of both Verilog HDL and VHDL, along with explanation of System Verilog concepts. You will also understand the Test Benches, FPGA ASICs, FPGA Testing as well as FPGA Design Flows & Design Tools.

This course will help you become an electronics/digital circuits engineer.

Course Objectives

Learn concepts of Design for Testability, Fault Detection & Simulation

Understand the Verilog Language principles

Design digital systems as part of a wider system design framework

Examine the construction and functioning of semiconductor memory, which are commonly utilized in application-specific digital systems.

Grasp Digital IC Design Concepts

Learn VHDL & Verilog and their application in designing & simulating the behavior of digital systems & circuits

Understand how VHDL/Verilog is used to design various digital ICs

Perform timing verification, boundary scan, etc.

Define State Machines, RTL Design

Learn FPGA Testing, FPGA Design Flows & Tools

Digital System Design with VHDL & Verilog – Course Syllabus

Design for Testability

Fault Simulation

Test Vector Generation and IDDQ

Timing Verification

Boundary Scan

VHDL

Sequential Design

State Machines

State Reduction & Assignment

State Machine Design & Analysis

RTL Systems & RTL Design

Verilog

System Verilog

Test Benches

Introduction to FPGA

FPGA Testing

FPGA Design Flows & Design Tools

Who this course is for:

ASIC Design Engineers

Electronics/Embedded Engineers

Anyone aspiring for a career in Electronics / Digital Circuits / RTL / ASIC

Digital Design Engineers – RTL, ASIC, VHDL, Verilog, SystemVerilog

RTL Design Engineers

Beginners & newbies interested in Electronics / Digital Systems Design

VHDL & Verilog – Designer Programmers

Senior Design Verification Engineers

Digital Design Verification / Test Engineers

FPGA/ASIC Design Engineers

Firmware Engineers – VHDL FPGA

FPGA Hardware Design Engineers

FPGA Verification Engineers

Physical Design Engineers

Password/解压密码www.tbtos.com

Password/解压密码www.tbtos.com