Mentor Graphics Corporation, a Siemens business, is pleased to announce the availability of Questa Formal 2021.1. This solution find obscure bugs, increasing design confidence through exhaustive analysis, before simulation test environments are available, and also boost productivity and functional verification quality by targeting verification tasks that are difficult to complete.

2021.1 Release Notes

Major New Features in 2021.1

Version 2021.x releases have significant enhancements and changes compared with the 2020.x series of releases.

New Tcl Commands

– cdc promote constraint – new directive to change the promotion attributes of specified CDC constraint.

– resetcheck preference isolation – new directive to set preferences for isolation strategies.

New Reset Check Schemes/Checks

– reset_as_data – asynchronous set or reset signal is connected to data pin.

New Lint Checks

– case_small – case statement has fewer case items.

– comment_density_low – comment density of a design file is less than the specified limit.

– func_arg_array_constrained – function argument is a constrained array.

– module_has_multi_clks – multiple sequential blocks use the same clock.

– net_decl_with_assign – net is declared and assigned in the same statement

– package_disallowed – use of the specified package is not allowed.

– package_name_not_standard – package name does not follow standard naming rules.

– pragma_disallowed – use of the specified pragma is not allowed.

– reg_reset_value_disallowed – register is assigned a reset value, which is not allowed.

– sync_control_is_internal – synchronous control signal is internally generated.

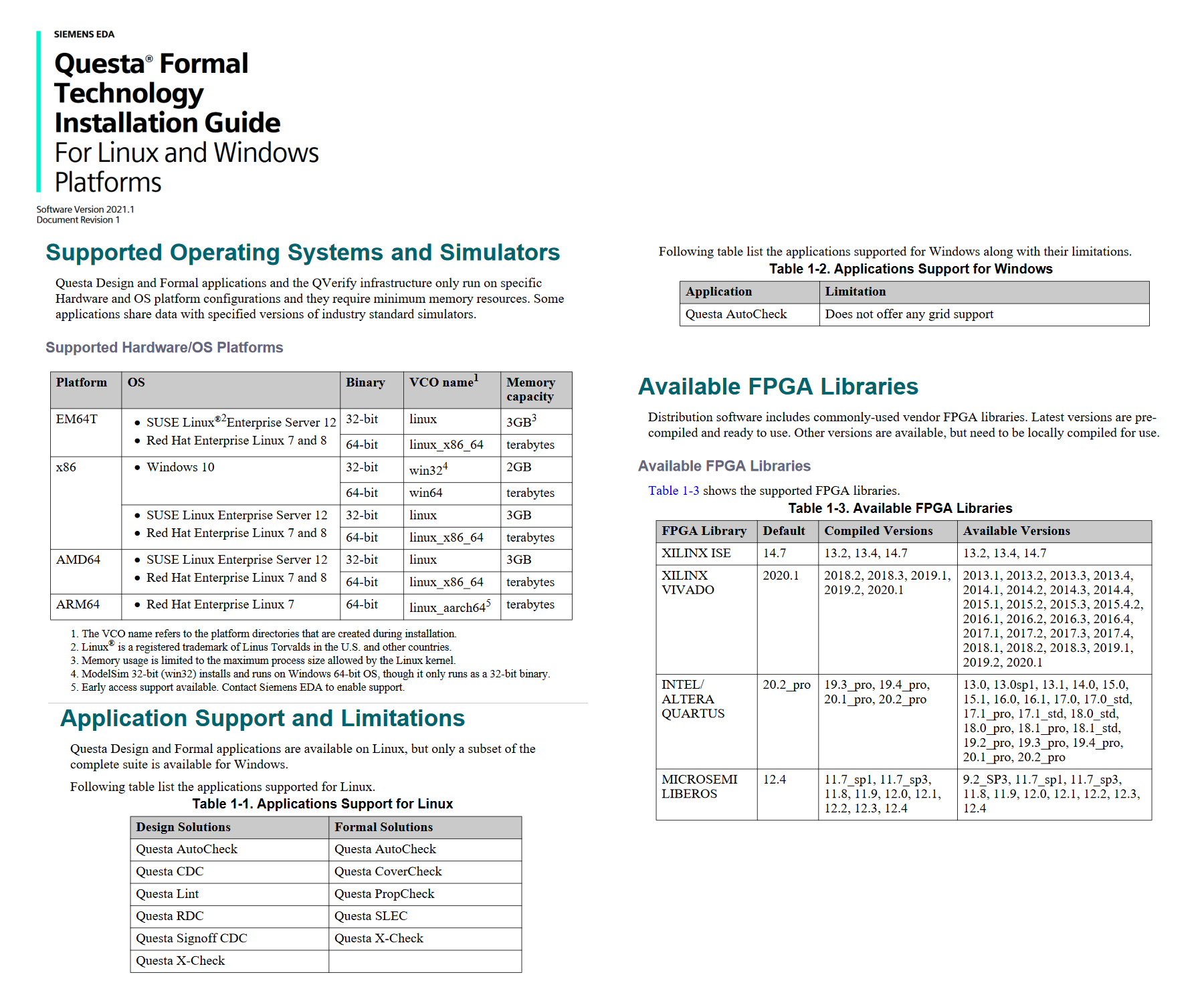

The Questa verification solution from Siemens EDA, a part of Siemens Digital Industries Software, continues to evolve in response to the growing complexity of SoC designs. Besides the sheer size of designs, the inclusion of multiple embedded processors and advanced interconnect systems, increasing software content and the configurability required by multi-platform based designs require a functional verification solution that unifies a broad arsenal of verification solutions.

Questa lets you apply CDC verification, formal verification, mixed-signal verification, portable stimulus, and other powerful technologies to maximize the effectiveness of your verification at the block- and subsystem-level so your system-level verification can focus on system-level functionality, including software, without having to worry about lower-level bugs taking away from your productivity. No one wants to compromise product quality. However, time-to market pressures dominate SoC projects. To deliver quality within schedule requires improving the time to achieve coverage and quality goals and improving debug productivity.

Questa Formal Apps statically analyze a design’s behavior with respect to a given set of properties; then exhaustively explore all possible input sequences in a breadth-first search manner. This uncovers design errors that would otherwise be missed or are impractical to find with simulation-based methods.

Questa Formal Apps boost verification efficiency and design quality by exhaustively addressing verification tasks that are difficult to complete with traditional methods, and they don’t require formal or assertion-based verification experience.

Properties are synthesized from a combination of automatic RTL design analysis and a high-level specification of design intent. The generated properties are then exhaustively verified with formal analysis engines.

The Questa Formal App suite includes applications to address tasks such as: static and conditional connectivity checking, secure path integrity checking, unreachable code identification, X-state propagation, state-space analysis, and register verification. Additionally, the Questa Sequential Logic Equivalence Checking (SLEC) App uses formal methods to perform exhaustive comparisons between inputs to reveal any behavioral discrepancies that could arise in clock gating, ECO integration, re-pipelining, or fault mitigation logic.

Mentor Graphics Corporation, a Siemens business, is a world leader in electronic hardware and software design solutions, providing products, consulting services, and award-winning support for the world’s most successful electronic, semiconductor, and systems companies. Corporate headquarters are located at 8005 S.W. Boeckman Road, Wilsonville, Oregon 97070-7777.

Product: Mentor Questa Formal

Version: 2021.1

Supported Architectures: x64

Website Home Page : https://eda.sw.siemens.com/

Languages Supported: english

System Requirements: PC *

Size: 1.4 Gb

Password/解压密码www.tbtos.com

转载请注明:0daytown » Mentor Questa Formal 2021.1