Published 1/2023

MP4 | Video: h264, 1280×720 | Audio: AAC, 44.1 KHz

Language: English | Size: 5.45 GB | Duration: 8h 33m

with access to Project Files and Code

What you’ll learn

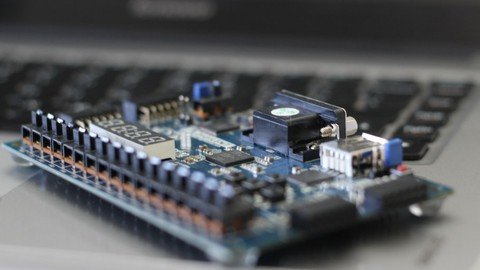

Learn Verilog from scratch on Vivado platform

Design finite state machines (FSM) with real world application such as games

Learn Verilog to establish an interface between Vivado and FPGA, and implement design onto FPGA

Create testbench files, simulate and analyze logic circuit diagrams to verify the logic

Requirements

No programming experience required. The course will start at a very basic level and slowly transitions to an intermiediate to advance level.

Description

Digital circuits are the foundation upon which the computers, cell phones, and calculators we use every day are built. This course explores these foundations using modern digital design techniques to design, implement and test digital circuits ranging in complexity from basic logic gates to state machines that perform useful functions like calculations, counting, timing, and a host of other applications. Students will learn modern design techniques using a hardware description language (HDL) such as Verilog to design, simulate and implement logic systems consisting of basic gates, adders, multiplexers, latches, and counters. The function and operation of programmable logic devices, such as field programmable gate arrays (FPGAs), will be described and discussed in terms of how an HDL logic design is mapped and implemented. Learn about Verilog as a beginner. In this course, we will learn about the basics of Verilog and how we can use it in the Vivado environment to generate combinational and sequential designs. We’ll design finite state machines with real-world applications such as vending machines, T20 Cricket Games, Counters, etc., and implement them onto an FPGA board. We’ll learn about the basic understanding of generating slow clocks, shift registers, flip flops, and counters to design basic-intermediate-advance-level FPGA projects. In addition, we’ll generate testbench files to validate the logic and analyze the functionality of the design. The course will cover an explanation of the code line by line that students can follow and replicate on their own board while they watch the video.Access to project files, supporting material, and code is included in the courseCome and join the course and become an expert on Verilog and FPGAs.

Overview

Section 1: Learn Verilog Basics – Basys 3 FPGA Board

Lecture 1 FPGA for BEGINNERS➟How to Get Started with Basys 3 Board and Vivado?

Lecture 2 Creating a testbench file and simulating your logic design

Lecture 3 Verilog Description of D Flip Flop and Vivado Simulation

Lecture 4 Verilog Description of JK Flip Flop and Vivado Simulation

Lecture 5 Verilog Description of T Flip Flop and Vivado Simulation

Lecture 6 Designing a Basic Calculator | Verilog | Step-by-Step Instructions

Lecture 7 Design a Slow Clock on an FPGA Board? | Verilog | Step-by-Step Instructions

Lecture 8 Debouncing Pushbutton | Verilog | Step-by-Step Instructions

Lecture 9 Binary to BCD Conversion | Basys 3 FPGA Board | Step-by-Step Instructions

Section 2: FPGA Projects

Lecture 10 Design a Home Alarm System | Verilog | Step-by step Instructions

Lecture 11 Design a Car Parking Slot System | Verilog | Step-by-Step Instructions

Lecture 12 Design a Digital Safe System | Verilog | Step-by-Step Instructions

Lecture 13 LFSR Counter | Verilog | Step-by-Step Instructions

Lecture 14 Part 1: UART-TxD Serial Communication| Verilog ➟ Step-by-Step Instructions

Lecture 15 Part 2: UART-RxD Serial Communication ➟ Step-by-Step Instructions

Lecture 16 Scrolling LEDs | DIY Billboard Display | Verilog | Step-byStep Instructions

Lecture 17 T20 Cricket Game onto an FPGA Board | Verilog | Step-byStep Instructions

Lecture 18 Whack-a-Mole Game | Verilog | Step-byStep Instructions

Lecture 19 Vending Machine| Verilog | Step-byStep Instructions

Digital Electronics Students,FPGA beginners,Verilog VHDL beginners,Electrical Engineering Students,FPGA Learners,FPGA Projects

Password/解压密码www.tbtos.com

转载请注明:0daytown » Digital System Design With Fpga Using Verilog