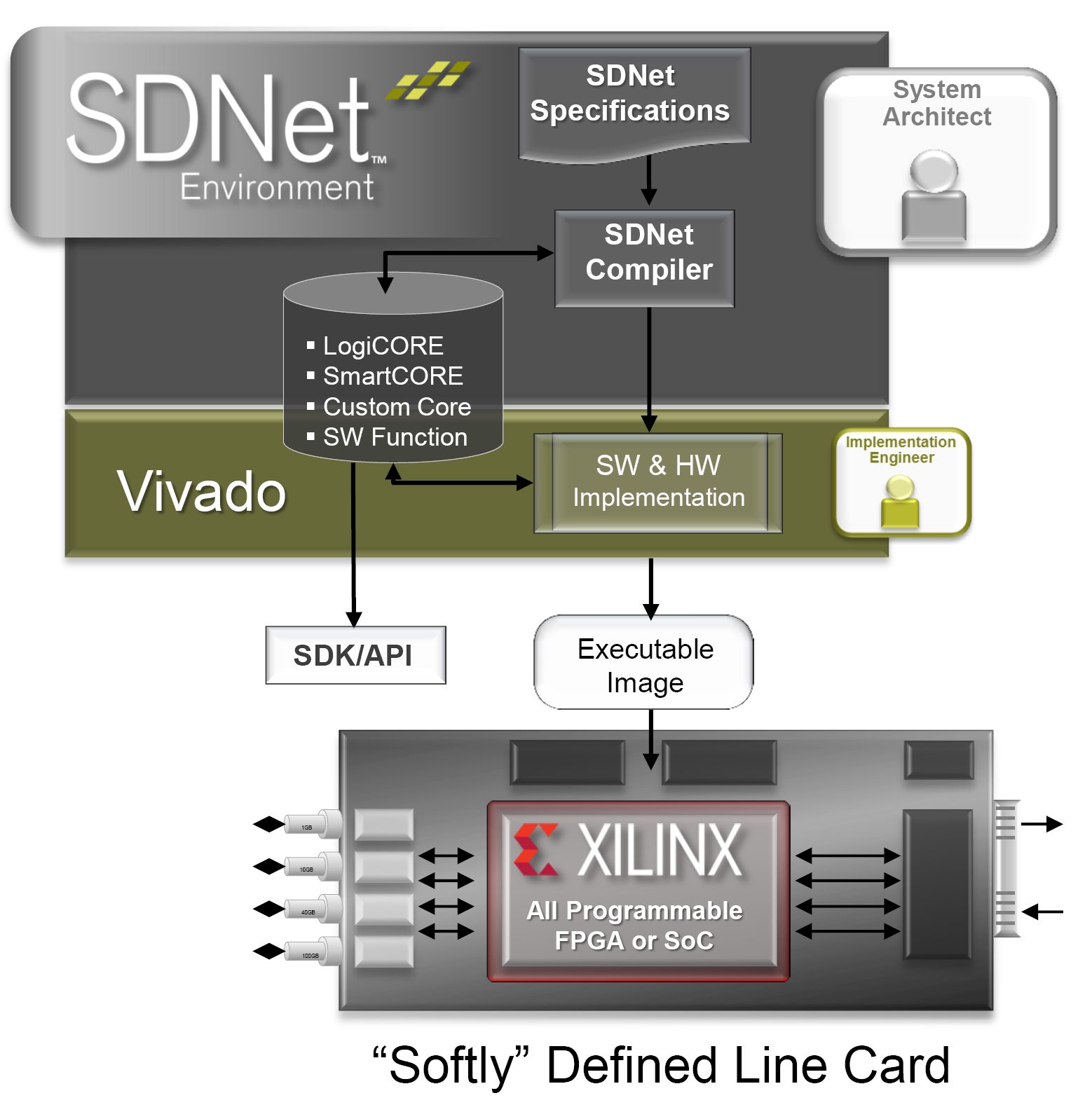

SDNet的最大特点之一是指定内容但不规定方式。也就是说,SDNet将不会关心怎样(How)实现一个网络规划,而是更在意如何通过软件的方式实现系统级人员的需要(What),比如包的解析、编辑、调节、查找等。另一方面,赛灵思的SDNet支持系统架构者通过新型的高级网络抽象语言(高级包处理规范)自动生成数据平面功能,而无需了解底层设备架构或掌握复杂的硬件编程语言,非常适合不具备FPGA专业知识的计算机专业科研人员

在SDNet的具体使用过程中,系统架构师和技术工程师实现了清晰的任务划分。前者负责定义SDNet规格,并使用SDNet编译器生成具体要求;后者则根据要求实现优化,包括具体的器件型号、与IT系统进行集成等。

The SDNet Development Environment for networking, in conjunction with Xilinx FPGA and SoC devices, allows for the creation of next-generation hardware-accelerated software-defined networks.

SDNet supports packet processing functionality with high throughput and low latency. It allows for game-changing differentiation through software-programmable data plane hardware with content intelligence that dynamically collaborates with control plane software. This addresses the performance, flexibility, and security challenges of modern content-oriented, intent-based, and zero-touch, networking.

SDNet finds applications in data plane acceleration across network switching, network slicing, data center networking, and multi-access edge computing (MEC), including Software Defined Networking (SDN) with Network Functions Virtualization (NFV) and network security (IPSec, SSL, NGFW etc.) use cases.

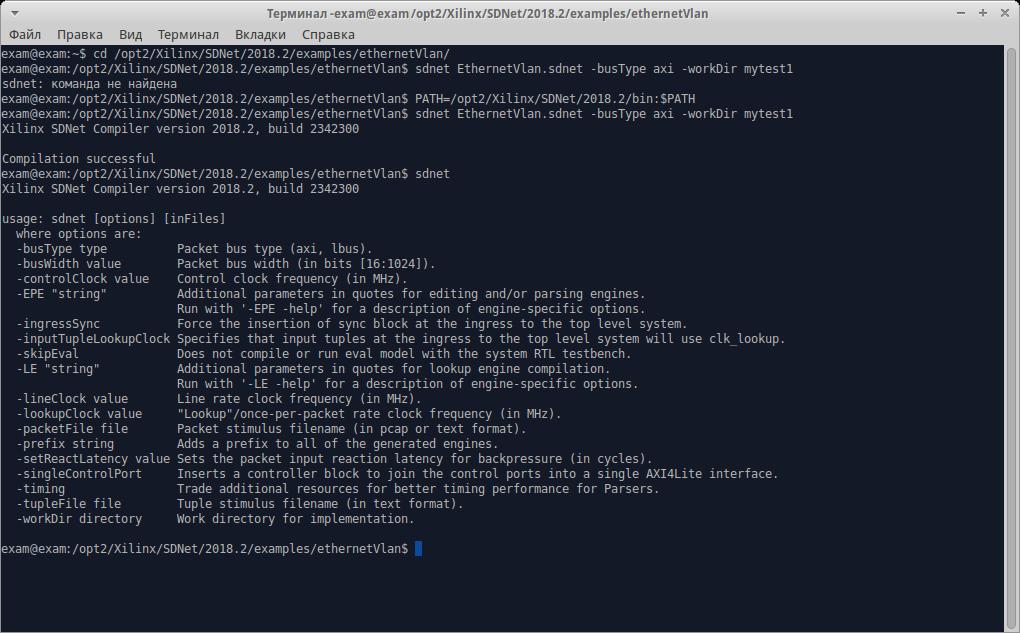

SDNet Compiler Release Notes – UG1018 (v2018.2) October 12, 2018:

– Minor updates to P4-SDNet.

– PX system building now flattens hierarchical design during compilation to fix an issue where systems could have tuple connections that could bypass subsystems.

– Fixed issue with Vivado® Design Suite simulation scripts.

– Updated XPM compatibility for newer versions of Vivado tools.

– Includes additional P4 example designs.

Known Issues

– Xilinx recommends using a common clock to drive the clk_lookup and clk_control inputs on lookup engines.

– For testbench simulation convenience, SDNet copies a version Vivado’s XPM IP (xpm_cdc.sv, xpm_memory.sv, and xpm_fifo.sv) into the same directory as the Verilog sources. However, in the case of running the Vivado implementation tools on the design, it might be necessary to either remove or replace these files before packaging the IP to avoid conflicts with other versions of these files. Vivado Design Suite provides its version of these files within the Xilinx\Vivado\2018.x\data\ip\xpm subdirectories.

Version: 2018.2 Build 2342300

Supported Architectures: x64

Supported Operating Systems: *

Software Prerequisites: For Windows operating systems, Vivado Design Suite 2017.3 or later is required for RTL simulation.

Password/解压密码-0daydown

Download rapidgator

https://rg.to/file/b5fa7f4cc85a30bf59d499065e4b296a/Xilinx_SDNet_2018.2.part1.rar.html

https://rg.to/file/c943bbc85019c07cd9e7b6207c232471/Xilinx_SDNet_2018.2.part2.rar.html

Download nitroflare

http://nitroflare.com/view/C1B85C0B0282AE4/Xilinx_SDNet_2018.2.part1.rar

http://nitroflare.com/view/E83AEFD6F56AC38/Xilinx_SDNet_2018.2.part2.rar

Download 百度云

你是VIP 1个月(1 month)赞助会员,

转载请注明:0daytown » Xilinx SDNet 2018.2